Wie war das denn bei Polaris und RDNA1, als es auch keine Highend-Variante gab - konnten die dennoch ihre Vorgänger übertrumpfen?

Schwierig, damals hat man ja irgendwie ein Chaos in den Produkten gehabt, da mischte sich Polaris (GCN4.0) und Vega (GCN 5.0) ja irgendwie völlig durcheinander, dazu HBM Modelle (VII) usw. Daher ist die Frage in meinen Augen nicht sinnvoll zu beantworten, denn die 5700XT und die Radeon VII waren meines Wissens nach auf Augenhöhe unterwegs was die Leistung angeht. Allerdings war die 5700XT die um längen bessere Karte, mit viel mehr Effizienz und einem unschlagbaren Preisvorteil. (419 EUR die 5700XT und 729 EUR die VII). Die VII kam aber eben gar nicht aus dem "Consumer" Sektor und wurde am Ende aus eine Professionellen Karte umgelabelt und daher fraglich, ob dies der geeignete Testkandidat wäre? Auf der anderen Seite war es ja quasi AMDs Titan und Nvidia misst sich ja auch heuer an ihrer 90er Serie die quasi die Titans abgelöst hat.

Aber entscheide selber! Die 5700XT war deutlich schneller und effizienter als die Vega64 (der eigentliche Vorgänger), im Vergleich zur sonderbaren VII war sie aber nicht schneller.

Falls nein, dann werd ich meine 6950 XT bis RDNA5 rocken

Sieht aktuell so aus, dass du dies problemlos tun kannst, sofern du nicht die Auflösungen wechselst und Raytracing nutzen möchtest, wird die 6900Xt noch eine Weile halten. Ich warte auch noch, NVs 4080/4090 sind mir aktuell zu teuer und die 7900XT ist einfach nicht schnell genug um einen Unterschied zu machen. Dazu sind nahezu alle aktuellen Games was das angeht auch recht genügsam, CB kann ich bedenkenlos spielen (nativ/ohne RT) und wenn ich nicht RT irgendwann doch noch gut finde (oder VR, was ich viel eher glaube) dann wird die 6900XT wahrscheinlich bis zur PS5 Pro gut hinkommen (erwarte erst da wieder echte Upgrades bei den Systemanforderungen).

Das der Yield der Hauptgrund für Chiplets ist, ... macht bei TSMC derzeit kaum Sinn.(der Yield ist gut)

Vorsichtig, mit der Aussage liegst du offensichtlich nicht gut, diese würde nur Sinn ergeben, wenn der Yield sehr sehr nahe 100% liegt, was er nicht tut! Das der Yield besser als erwartet ist ist sicher ein gutes Zeichen, aber eben überhaupt keines, dass ein kleinerer Chip nicht dennoch viel besser ist.

AMD sollte wirklich bis zur oberen Mittelklasse auf 1-Chipdesign setzen

Kommt halt drauf an, was obere Mittelklasse bedeutet? Früher war das mal die Kategorie 4060/4070 und da setzt AMD auf monolithische Designs.

Bei Nvidia hätte man sich den Wechsel auf Samsung wohl gespart, wenn man gewußt hätte, dass es eine Generation später wieder zurück geht.

Retroperspektivisch hat Nvidia doch alles richtig gemacht und würde das wahrscheinlich immer wieder so machen, man hat (mit exorbitanten Leistungsverbräuchen, die seltsamerweise damals niemanden interessiert haben) AMD die Stirn gehalten und wahnsinnige Gewinnmargen realisieren können mit Samsungs deutlich deutlich günstigerem Node. Nvidia würde wahrscheinlich nur aus heutiger Sicht keinen etwas teureren spezialisierten 5nm Node bei TSMC nutzen, sondern den ganz normalen, da AMD eben nicht mehr mithalten kann.

Bei AMD hätte man Vega wohl nicht mit HBM ausgestattet

Wobei HBM gut war und nicht das Problem, man brauchte Bandbreite und die hatte man damit eben erreicht, leider ist HBM immer noch zu teuer, sonst könnte ich mir sowas schon nochmal vorstellen, gerade HBM2e (1.844 GB/s bei 4 Stacks) ist ja schon nett und wenn HBM3 (3.276 GB/s bei 4 Stacks) verfügbar ist, da wirken die gerade einmal 1008 GB/s der 4090 schon mickrig gegen! Dabei wird HBM3 sogar weniger Energie aufnehmen als der aktuelle GDDR6X der 4090! Ich denke sogar, dass HBM ein wichtiger Schritt werden kann, HBM4 ist für 2026 angekündigt, mit dann über 6TB/s) und GDDR7 wird mit 384bit Interface auf "lediglich 1,5TB/s kommen, HBM3 ist also schon mehr als doppelt so schnell wie das noch erscheinende GDDR7!

Ich denke das Problem ist, dass HBM ein anderes Speicherinterface benötigt und dies nur für einen Chip nicht extra gebaut werden soll. Daher wird HBM aus dem Consumersegment herausgehalten, natürlich weil es am Ende in der Kombinantion, Speichercontroller, Interface und HBM zu teuer ist.

Das ist aber nicht der Auslieferungszustand der Karten, der war einfach schrecklich.

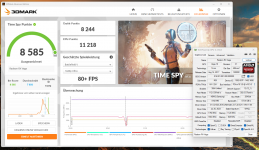

Sagt jemand über die 4090, dass es eine schreckliche Karte ist? Nö, obwohl der Auslieferungszustand mit 600W TDP wirklich grausam ist, so bekommen es die Leute ja recht simpel hin, die Karte in einen fast perfekten Zustand zu versetzen.