AW: Geforce-Grafikkarten: Nvidia über 7 Nanometer

Kannst Du die Zahlen noch mal präzisieren, denn die sehen nicht plausibel aus.

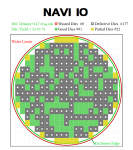

a) Du hast dich voraussichtlich bei der Benennung vertan, denn Du meintest wahrscheinlich "Navi 10" und nicht "Navi 12". Letzterer soll deutlich mehr CUs besitzen und ist daher leistungstechnisch deutlich über dem TU106 anzusetzen. Hinzu kommt, dass die Anzahl Dies/Wafer für Navi 12 vollkommen falsch wäre, denn der wird aktuell mit bis zu 64 CUs gehandelt und daher mit einer Fläche von 350 - 400 mm2.

b) Der Die/Wafer-Wert für den TU106 erscheint mit 149 Dies deutlich zu hoch. Ein plausiblerer Wert liegt gemäß Chipgröße bei um die 116 - 120 verwertbarer Dies/Wafer.

c) Die Defektrate für nVidia ist etwas optimistisch angesetzt, denn es handelt sich hierbei um einen dennoch vergleichsweise großen Chip. Realistischer wären 0,10/cm2, was in 65 % Yield resultiert und nur noch 76 vollständig funktionsfähigen Chips. Und ob nVidia/TSMC den trotz des gut eingefahrenen Prozesses erreicht ...?

d) Der Yield für Navi 10 (von Dir als Navi 12 benannt) ist viel zu optimistisch und verzerrt die gesamte Betrachtung. Bestenfalls wird der gleiche N7-Prozess wie für das Zen2-Chiplet verwendet oder aber der N7P, der vergleichbare Charakteristika hat. Ein realistischerer Wert von Dies/Wafer dürfte für Navi 10 bei bestenfalls um die 218 Dies/Wafer liegen. Nimmt man für das Zen2-Chiplet eine sehr guten Wert von 78 % Yield an (den man derzeit wahrs. eher nicht erreichen wird) und überträgt die Defektrate auf den GPU-Chip, kommt man auf einen Yield von bestenfalls 45 % und etwa 97 voll funktionsfähigen Dies/Wafer.

Letzterer Wert ist von nVidias TU106 gar nicht so weit weg, was schlicht daran liegt, dass hier ein alter, sehr gut eingefahrener Prozess mit einem sehr guten Yield gegen einen neuen/bleeding-edge Prozess verglichen wird.

Fehlerhafte Chips bedeuten aber bei GPU-Designs nicht automatisch, dass diese Dies wertlos sind, denn in vielen Fällen kann man CU/SM-Blöcke deaktivieren und den Die als ein kleineres Produkt verkaufen.

Schlussendlich dürfte diese Beobachtung hier auch ein Grund für nVidia's zögerliche Aussage zu einem neuen Prozess sein. Mit Blick auf HighEnd-Chips würde ich dennoch von einem Upgrade ausgehen (min. auf 10 nm), denn der TU102 hat bspw. in Bezug auf Fläche und Perf/Watt eine Grenze erreicht, die zwangsweise zusätzliche Recheneinheiten und damit Transistoren notwendig macht, insbesondere, wenn nVidia seine Zusage bzgl. einer (relativ gesehen) deutlich gesteigerten Raytracing-Leistung einhalten will. Derartige Zusagen sind ohne mehr Transistoren (also nur durch architektonische Umstellungen) kaum zu erreichen und daher werden die neuen HighEnd-Chips noch komplexer. Vom TU102 passen jetzt schon etwa nur 64 Dies überhaupt auf einen Wafer und selbst mit einem sehr guten Yield kommen dabei bestenfalls (und wahrscheinlich sehr optimistisch) 39 voll funktionsfähige Chips heraus. In diesem Bereich bleibt ein aktuellerer Prozess unvermeidbar, jedoch muss das nicht zwingend ein 7nm-Prozess werden. Einfach mal abwarten ...

nVidia wird nicht drumherum kommen ...

Kannst Du die Zahlen noch mal präzisieren, denn die sehen nicht plausibel aus.

a) Du hast dich voraussichtlich bei der Benennung vertan, denn Du meintest wahrscheinlich "Navi 10" und nicht "Navi 12". Letzterer soll deutlich mehr CUs besitzen und ist daher leistungstechnisch deutlich über dem TU106 anzusetzen. Hinzu kommt, dass die Anzahl Dies/Wafer für Navi 12 vollkommen falsch wäre, denn der wird aktuell mit bis zu 64 CUs gehandelt und daher mit einer Fläche von 350 - 400 mm2.

b) Der Die/Wafer-Wert für den TU106 erscheint mit 149 Dies deutlich zu hoch. Ein plausiblerer Wert liegt gemäß Chipgröße bei um die 116 - 120 verwertbarer Dies/Wafer.

c) Die Defektrate für nVidia ist etwas optimistisch angesetzt, denn es handelt sich hierbei um einen dennoch vergleichsweise großen Chip. Realistischer wären 0,10/cm2, was in 65 % Yield resultiert und nur noch 76 vollständig funktionsfähigen Chips. Und ob nVidia/TSMC den trotz des gut eingefahrenen Prozesses erreicht ...?

d) Der Yield für Navi 10 (von Dir als Navi 12 benannt) ist viel zu optimistisch und verzerrt die gesamte Betrachtung. Bestenfalls wird der gleiche N7-Prozess wie für das Zen2-Chiplet verwendet oder aber der N7P, der vergleichbare Charakteristika hat. Ein realistischerer Wert von Dies/Wafer dürfte für Navi 10 bei bestenfalls um die 218 Dies/Wafer liegen. Nimmt man für das Zen2-Chiplet eine sehr guten Wert von 78 % Yield an (den man derzeit wahrs. eher nicht erreichen wird) und überträgt die Defektrate auf den GPU-Chip, kommt man auf einen Yield von bestenfalls 45 % und etwa 97 voll funktionsfähigen Dies/Wafer.

Letzterer Wert ist von nVidias TU106 gar nicht so weit weg, was schlicht daran liegt, dass hier ein alter, sehr gut eingefahrener Prozess mit einem sehr guten Yield gegen einen neuen/bleeding-edge Prozess verglichen wird.

Fehlerhafte Chips bedeuten aber bei GPU-Designs nicht automatisch, dass diese Dies wertlos sind, denn in vielen Fällen kann man CU/SM-Blöcke deaktivieren und den Die als ein kleineres Produkt verkaufen.

Schlussendlich dürfte diese Beobachtung hier auch ein Grund für nVidia's zögerliche Aussage zu einem neuen Prozess sein. Mit Blick auf HighEnd-Chips würde ich dennoch von einem Upgrade ausgehen (min. auf 10 nm), denn der TU102 hat bspw. in Bezug auf Fläche und Perf/Watt eine Grenze erreicht, die zwangsweise zusätzliche Recheneinheiten und damit Transistoren notwendig macht, insbesondere, wenn nVidia seine Zusage bzgl. einer (relativ gesehen) deutlich gesteigerten Raytracing-Leistung einhalten will. Derartige Zusagen sind ohne mehr Transistoren (also nur durch architektonische Umstellungen) kaum zu erreichen und daher werden die neuen HighEnd-Chips noch komplexer. Vom TU102 passen jetzt schon etwa nur 64 Dies überhaupt auf einen Wafer und selbst mit einem sehr guten Yield kommen dabei bestenfalls (und wahrscheinlich sehr optimistisch) 39 voll funktionsfähige Chips heraus. In diesem Bereich bleibt ein aktuellerer Prozess unvermeidbar, jedoch muss das nicht zwingend ein 7nm-Prozess werden. Einfach mal abwarten ...

)

)