Du verwendest einen veralteten Browser. Es ist möglich, dass diese oder andere Websites nicht korrekt angezeigt werden.

Du solltest ein Upgrade durchführen oder einen alternativen Browser verwenden.

Du solltest ein Upgrade durchführen oder einen alternativen Browser verwenden.

Bilderthread CPU ***Bilderthread***

- Ersteller der8auer

- Erstellt am

dergunia

Komplett-PC-Aufrüster(in)

masterX244

Freizeitschrauber(in)

egert217

PCGHX-HWbot-Member (m/w)

Zuletzt bearbeitet:

egert217

PCGHX-HWbot-Member (m/w)

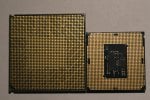

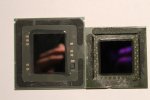

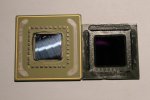

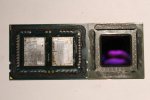

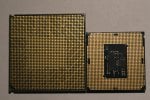

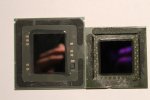

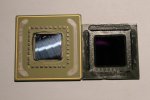

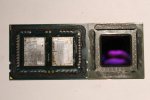

Habe jetzt auch die Konkurenz des Itanium fotografiert und delidded (von Links nach rechts):

1: Itanium 9340 4C/8T 1,6GHz 65nm process 726mm^2 DIE 185W TDP

2: IBM Power 7 8C/32T 3,0GHz 45nm process 590mm^2 DIE TDP unknown

3: ORACLE SPARC T3 16C/128T 1,65GHz 40nm process 400mm^2 DIE TDP unkown

4: AMD Opteron 6128 8C/8T 2,0GHz 45nm process 2x346=692mm^2 DIEs 115W TDP

5: Intel Xeon X6550 8C/16T 2,0GHz 45nm process 697mm^2 DIE 130W

1: Itanium 9340 4C/8T 1,6GHz 65nm process 726mm^2 DIE 185W TDP

2: IBM Power 7 8C/32T 3,0GHz 45nm process 590mm^2 DIE TDP unknown

3: ORACLE SPARC T3 16C/128T 1,65GHz 40nm process 400mm^2 DIE TDP unkown

4: AMD Opteron 6128 8C/8T 2,0GHz 45nm process 2x346=692mm^2 DIEs 115W TDP

5: Intel Xeon X6550 8C/16T 2,0GHz 45nm process 697mm^2 DIE 130W

masterX244

Freizeitschrauber(in)

Löschzwerg

BIOS-Overclocker(in)

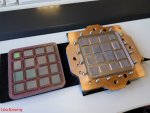

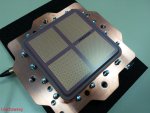

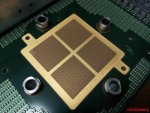

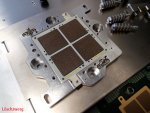

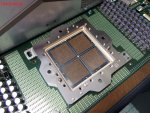

Hier das CPU MCM eines alten, defekten IBM z9 Mainframe. Leider nur Bilder vom Smartphone... mit DSLR folgen irgendwann.

Alle verbauten DIEs sind im 90nm SOI Verfahren hergestellt. Das MCM ist 95 x 95 (mm) Groß und besitzt 127 Lagen aus Glas-Keramik. Die Leiterbahnen (verteilt auf 10 Lagen Kupfer) haben eine Gesamtlänge von ca. einem halben Kilometer.

Das MCM hat:

8x PU - "Processing Unit"

2x MSC - "Memory Storage Control"

4x SD - "System Data"

1x SC - "Storage Control"

1x CLK - "Clock"

PU - "Processing Unit":

Ein Dual-Core Prozessor mit 121 Mio Transistoren auf 15.78 x 11.84 (mm). Gesamt 512KB L1-Cache (256KB I-Cache und 256KB D-Cache). Der Takt beträgt 1.7GHz.

MSC - "Memory Storage Control":

24 Mio Transistoren auf 14.31 x 14.31 (mm). Regelt den Zugriff zu den Hauptspeicher DIMMs und dient als Schnittstelle zum L2 Cache (SD). Zudem regelt der MSC den L2 Zugriff auf und von den MBAs (Memory Bus Adapter) für Verbindungen außerhalb des Systemboards.

SD - "System Data":

660 Mio Transistoren auf 15.66 x 15.40 (mm). Hierbei handelt es sich um einen L2-Cache Chip. Gesamt sind es pro MCM 40MB an L2-Cache.

SC - "Storage Control":

162 Mio Transistoren auf 16.41 x 16.41 (mm). Dient als "Switch" für alle L2-Cache Chips (SD) des jeweiligen MCM und ebenso als L2-Schnittstelle für weitere MCM auf zusätzlichen Systemboards (Verbindung über einen Ringbus; Bis zu 4x Systemboards sind möglich).

CLK - "Clock":

Taktgeber des MCM und ETR Empfänger (External Time Reference). Synchronisation ist extrem wichtig.

Alle verbauten DIEs sind im 90nm SOI Verfahren hergestellt. Das MCM ist 95 x 95 (mm) Groß und besitzt 127 Lagen aus Glas-Keramik. Die Leiterbahnen (verteilt auf 10 Lagen Kupfer) haben eine Gesamtlänge von ca. einem halben Kilometer.

Das MCM hat:

8x PU - "Processing Unit"

2x MSC - "Memory Storage Control"

4x SD - "System Data"

1x SC - "Storage Control"

1x CLK - "Clock"

PU - "Processing Unit":

Ein Dual-Core Prozessor mit 121 Mio Transistoren auf 15.78 x 11.84 (mm). Gesamt 512KB L1-Cache (256KB I-Cache und 256KB D-Cache). Der Takt beträgt 1.7GHz.

MSC - "Memory Storage Control":

24 Mio Transistoren auf 14.31 x 14.31 (mm). Regelt den Zugriff zu den Hauptspeicher DIMMs und dient als Schnittstelle zum L2 Cache (SD). Zudem regelt der MSC den L2 Zugriff auf und von den MBAs (Memory Bus Adapter) für Verbindungen außerhalb des Systemboards.

SD - "System Data":

660 Mio Transistoren auf 15.66 x 15.40 (mm). Hierbei handelt es sich um einen L2-Cache Chip. Gesamt sind es pro MCM 40MB an L2-Cache.

SC - "Storage Control":

162 Mio Transistoren auf 16.41 x 16.41 (mm). Dient als "Switch" für alle L2-Cache Chips (SD) des jeweiligen MCM und ebenso als L2-Schnittstelle für weitere MCM auf zusätzlichen Systemboards (Verbindung über einen Ringbus; Bis zu 4x Systemboards sind möglich).

CLK - "Clock":

Taktgeber des MCM und ETR Empfänger (External Time Reference). Synchronisation ist extrem wichtig.

Anhänge

-

IMG_20180724_125803.jpg668,6 KB · Aufrufe: 93

IMG_20180724_125803.jpg668,6 KB · Aufrufe: 93 -

IMG_20180724_125733.jpg680,6 KB · Aufrufe: 84

IMG_20180724_125733.jpg680,6 KB · Aufrufe: 84 -

IMG_20180724_102300.jpg856,7 KB · Aufrufe: 85

IMG_20180724_102300.jpg856,7 KB · Aufrufe: 85 -

IMG_20180724_102247.jpg845,1 KB · Aufrufe: 86

IMG_20180724_102247.jpg845,1 KB · Aufrufe: 86 -

IMG_20180724_101937.jpg877,2 KB · Aufrufe: 87

IMG_20180724_101937.jpg877,2 KB · Aufrufe: 87 -

IMG_20180724_101927.jpg748,1 KB · Aufrufe: 71

IMG_20180724_101927.jpg748,1 KB · Aufrufe: 71 -

IMG_20180724_101720.jpg851,8 KB · Aufrufe: 72

IMG_20180724_101720.jpg851,8 KB · Aufrufe: 72 -

IMG_20180724_101710.jpg819,2 KB · Aufrufe: 67

IMG_20180724_101710.jpg819,2 KB · Aufrufe: 67 -

IMG_20180724_101557.jpg980,9 KB · Aufrufe: 87

IMG_20180724_101557.jpg980,9 KB · Aufrufe: 87 -

IMG_20180724_101510.jpg922,1 KB · Aufrufe: 71

IMG_20180724_101510.jpg922,1 KB · Aufrufe: 71 -

IMG_20180724_101457.jpg683,8 KB · Aufrufe: 64

IMG_20180724_101457.jpg683,8 KB · Aufrufe: 64 -

IMG_20180719_115103.jpg699,7 KB · Aufrufe: 75

IMG_20180719_115103.jpg699,7 KB · Aufrufe: 75 -

IMG_20180719_111333.jpg906,4 KB · Aufrufe: 112

IMG_20180719_111333.jpg906,4 KB · Aufrufe: 112

Löschzwerg

BIOS-Overclocker(in)

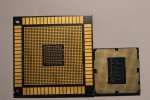

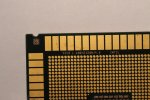

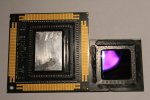

Mein aktueller Neuzugang, eine VIA Eden X3 L4500 CPU

Wie der Name schon andeutet eine Triple-Core CPU. Ein MCM aus zwei VIA Nano X2 (Dual Core Nano "CN"; Isaiah Architektur; 40nm Fertigung), wobei ein Kern deaktiviert ist. Die Taktfrequenz liegt bei 1,4GHz.

Die CPU arbeitet auf einem Mainboard mit VIA VN1000 Chipsatz (S3 Graphics Chrome 520 IGP).

Wie der Name schon andeutet eine Triple-Core CPU. Ein MCM aus zwei VIA Nano X2 (Dual Core Nano "CN"; Isaiah Architektur; 40nm Fertigung), wobei ein Kern deaktiviert ist. Die Taktfrequenz liegt bei 1,4GHz.

Die CPU arbeitet auf einem Mainboard mit VIA VN1000 Chipsatz (S3 Graphics Chrome 520 IGP).

Anhänge

Strikeeagle77

Komplett-PC-Aufrüster(in)

Ui, einige seltene Schätzchen dabei, aber dann doch irgendwie alles Jungspunde, finde ich ...

Letzterer Chip mit Goldcap ganz unten darf wohl kaum als CPU definiert werden, ist jedoch der älteste aus meiner Sammlung,

stammt aus der Woche meiner Geburt. KW15 /1977

Bei Interesse krame ich gerne mal meine 486er und SuperSockel7 Sammlung hervor (inkl. einiger Chomper-XT). Die sind aber etwas weiter weggepackt.

Letzterer Chip mit Goldcap ganz unten darf wohl kaum als CPU definiert werden, ist jedoch der älteste aus meiner Sammlung,

stammt aus der Woche meiner Geburt. KW15 /1977

Bei Interesse krame ich gerne mal meine 486er und SuperSockel7 Sammlung hervor (inkl. einiger Chomper-XT). Die sind aber etwas weiter weggepackt.

Anhänge

Zuletzt bearbeitet:

Christoph1717

Freizeitschrauber(in)

ich habe im Schrank noch einen alten Video Umschalter mit BNC Buchsen gefunden.

Vor vielen Jahren habe ich ein Praktikum bei Schott in Mainz gemacht und am Ende gab es eine Gelegenheit von den ausgemusterten Sachen was mit zu nehmen.

Falls zufällig jemand Intresse an dem Kasten haben solte, noch ist er zu verschenken. Einfach mal PM schreiben. Nächstes Jahr werde ich es wohl entsorgen, falls ich Platz für was besseres brauch (:

Vor vielen Jahren habe ich ein Praktikum bei Schott in Mainz gemacht und am Ende gab es eine Gelegenheit von den ausgemusterten Sachen was mit zu nehmen.

Falls zufällig jemand Intresse an dem Kasten haben solte, noch ist er zu verschenken. Einfach mal PM schreiben. Nächstes Jahr werde ich es wohl entsorgen, falls ich Platz für was besseres brauch (:

Anhänge

Zuletzt bearbeitet:

Essigwurst

Schraubenverwechsler(in)

LaCain1337

PC-Selbstbauer(in)

loltheripper

Software-Overclocker(in)

Xeon E7-4860 10 Kerner Westmere-EX für LGA 1567

Und mein Profilbild, AMD Opteron 6272 ES Bulldozer. Hatte mal einen defekten bekommen und den dann geköpft. Sieht nach infinity fabric 1.0 aus.https://uploads.tapatalk-cdn.com/20181201/16a1c3a2c78a9c3be3649bbbc785cd11.jpghttps://uploads.tapatalk-cdn.com/20181201/0478a93b47039d284239f9cc5b052fa8.jpghttps://uploads.tapatalk-cdn.com/20181201/7dae9318cbea4ab134a1117f7f44cd9e.jpg

Und mein Profilbild, AMD Opteron 6272 ES Bulldozer. Hatte mal einen defekten bekommen und den dann geköpft. Sieht nach infinity fabric 1.0 aus.https://uploads.tapatalk-cdn.com/20181201/16a1c3a2c78a9c3be3649bbbc785cd11.jpghttps://uploads.tapatalk-cdn.com/20181201/0478a93b47039d284239f9cc5b052fa8.jpghttps://uploads.tapatalk-cdn.com/20181201/7dae9318cbea4ab134a1117f7f44cd9e.jpg

Ähnliche Themen

- Antworten

- 14

- Aufrufe

- 7K

- Antworten

- 27

- Aufrufe

- 10K

- Antworten

- 3

- Aufrufe

- 2K

:

: