Jetzt ist Ihre Meinung gefragt zu TSMC ab 2020 mit 5-nm-Fertigung

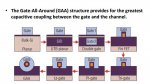

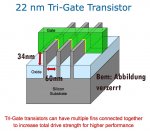

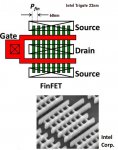

TSMC hat seine Zahlen vorgestellt und dabei einen Blick in die Zukunft gewagt. Ab 2018 soll in 7 nm Finfet, ab 2020 in 5 nm Finfet produziert werden. Die Taiwaner haben eigenen Angaben nach gute Erfolge mit EUV-Lithographie gehabt. Mitbewerber zeigen, dass die Ziele sportlich sind.

Bitte beachten Sie: Der Kommentarbereich wird gemäß der Forenregeln moderiert. Allgemeine Fragen und Kritik zu Online-Artikeln von PC Games Hardware sind im Feedback-Unterforum zu veröffentlichen und nicht im Kommentarthread zu einer News. Dort werden sie ohne Nachfragen entfernt.

Zurück zum Artikel: TSMC ab 2020 mit 5-nm-Fertigung

Zurück zum Artikel: TSMC ab 2020 mit 5-nm-Fertigung

TSMC hat seine Zahlen vorgestellt und dabei einen Blick in die Zukunft gewagt. Ab 2018 soll in 7 nm Finfet, ab 2020 in 5 nm Finfet produziert werden. Die Taiwaner haben eigenen Angaben nach gute Erfolge mit EUV-Lithographie gehabt. Mitbewerber zeigen, dass die Ziele sportlich sind.

Bitte beachten Sie: Der Kommentarbereich wird gemäß der Forenregeln moderiert. Allgemeine Fragen und Kritik zu Online-Artikeln von PC Games Hardware sind im Feedback-Unterforum zu veröffentlichen und nicht im Kommentarthread zu einer News. Dort werden sie ohne Nachfragen entfernt.

.

.