TSMC Node also...

Heisst das dann, dass Intel die Fertigungsprobleme immer noch nicht im Griff hat und mit den großen CPUs die hohen Taktraten nicht hinbekommt?

Nein, dass heißt es nicht. Aktuell sieht es eher danach aus, als wenn Intel seine Prozess-Roadmap einhalten und mit 18A in 2025 dann TSMC gar überholen wird.

nVidia's kürzliche Aussage zu "

gut/vielversprechend aussehenden Testchips" bezog sich übrigens auf in 18A gefertigte Chips. Intel fertigt diese bereits seit etwa Ende 2022 für seine Foundry-Interessenten um den Entwicklungsprozess zu dokumentieren und nachzuweisen, dass sie bzgl. der Entwicklung on-track sind, denn die Interessenten müssen sich

jetzt so langsam festlegen. (

Heißt auch, dass die nVidia-Aussage nichts mit der 2024er-GPU-Gen zu tun hat, was so mancher Artikel leider nicht explizit herausstrich. So eine Umstellungen bzgl. der Foundry und der damit verbundenen Tools kostet viel Zeit und Vorlauf.)

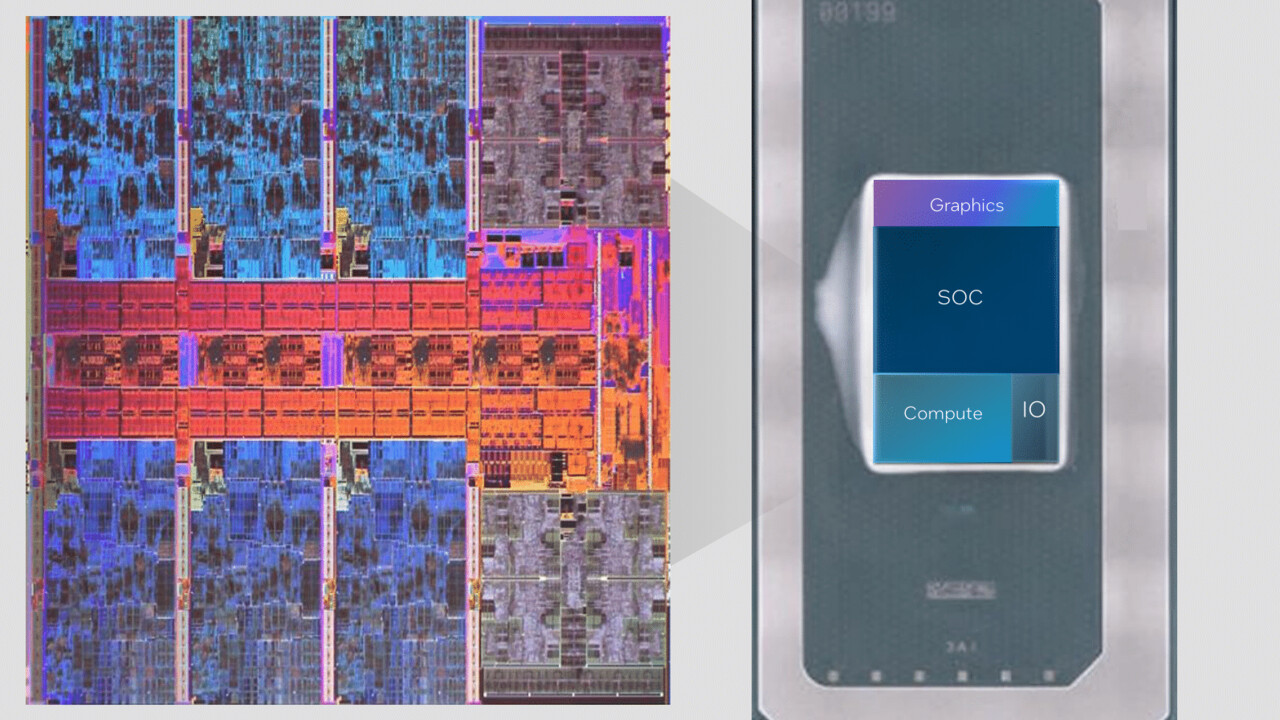

Intel wird Arrow Lake bei den mobilen Chips (

die für Intel übrigens mittlerweile deutlich wichtiger sind) in Intel 20A fertigen. bzw. konkret dreht sich in dieser Diskussion dann alles um das sogenannte Compute Tile, dass die Rechenkerne und den Cache bis zum L3$ implementiert. Wenn es gut bei Intel laufen sollte, könnte gar bereits deren 20A leicht die Nase vorn haben vor TSMCs 3 nm, die zu diesem Zeitpunkt bestenfalls noch höher takten können, was Intel dann aber mit einer weiteren Prozessiteration nachziehen kann und was hier für Mobile weniger eine Rolle spielt, d. h. man wird hier bereits mit einem mindestens gleichwertigen Prozess aufwarten.

Dass der neuetes Prozess nicht gleich skyrocketing den Takt hochschrauben kann und nun 7 GHz errreichen wird, ist dagegen vollkommen normal, zumal man hier gegen einen mittlerweile extrem optimierten Intel 7 vergleichen wird (

bei dem zudem gemäß aktueller Policy in einigen Anwendungsbereichen der Verbrauch offensichtlich als irrelevant betrachtet wird

) Weiterhin kommt hinzu, dass die Massenfertigung in 20A gerade erst mal mit ARL anlaufen wird, d. h. man wird gleichzeitig noch begrenzte Kapazitäten haben, die erst mit der Zeit ausgebaut werden, d. h. auch die Kapazitätsfrage könnte hier hineinspielen, sodass man noch einen weiteren Grund hat sich mit TSMC zu behelfen.

Ergänzend muss zudem Intel auch die bei TSMC gebuchten Kapazitäten und Ressourcen nutzen, denn die haben hier ein sehr umfangreiches Fertighungsabkommen geschlossen und TSMCs wäre es vollkommen egal, wenn Intel bspw. rein aus Prestige-Gründen, selbst wenn sie es denn könnten, nur in der eigenen Fertigung ihre Kernprodukte fertigen wollen würden ... bezahlen müsste Intel TSMC so oder so

Am Ende werden hier zweifelsfrei mehrere Aspekte hineinspielen, die wichtigsten dürften vermutlich ein anfänglich noch etwas begrenzter Takt i. V. z. den eigenen (überreizten) Topprodukten sowie die Fertigungskapazitäten sein.

Bezüglich dem Desktop wäre AMD damit aber bereits im Nachteil *), denn das reguläre Zen5-CCD wird nur in einem 4 nm-Prozess gefertigt werden (

was immer noch eine 5 nm-Iteration ist; erst die 3 nm-Prozesse stellen einen Full-Node-Sprung dar). AMD wird die teuere 3 nm-Fertigung bei CPUs nur beim Zen5c-CCD (

etwas langsamere Kerne, dafür eine höhere Dichte und bessere Effizienz; zudem vermutlich einigen APUs) anwenden und hier ist immer noch unklar, ob es in der kommenden Gen eine Hybrid-CPU der Art 1xZen5 + 1xZen5c = 24 Kerne geben wird. Undenkbar wäre das nicht, denn wenn ARL wirklich mit derart vielen E-Kernen kommt (

sehe ehrlich gesagt auf dem Desktop eher weniger Bedarf dafür zurzeit), dann würde das einen beträchtlichen Druck auf AMD aufbauen und MT-technisch hätte man Intel mit einem regulären 16-Kerner nichts entgegenzustellen.

*) ARL wird vermutlich im N3E (2nd Gen 3 nm) gefertig werden bzgl. des Compute Tiles und zudem ebenso große (

oder gar etwas größere) IPC-Zugewinne aufgrund des grundlegend überarbeiteten Architekturdesign mitbringen.

Ob Intel hier bzgl. dem Desktop-Gaming (

das in Intels Sichtweise zweifellos von geringerer Relevanz ist) das Design dann noch zusätzlich um den

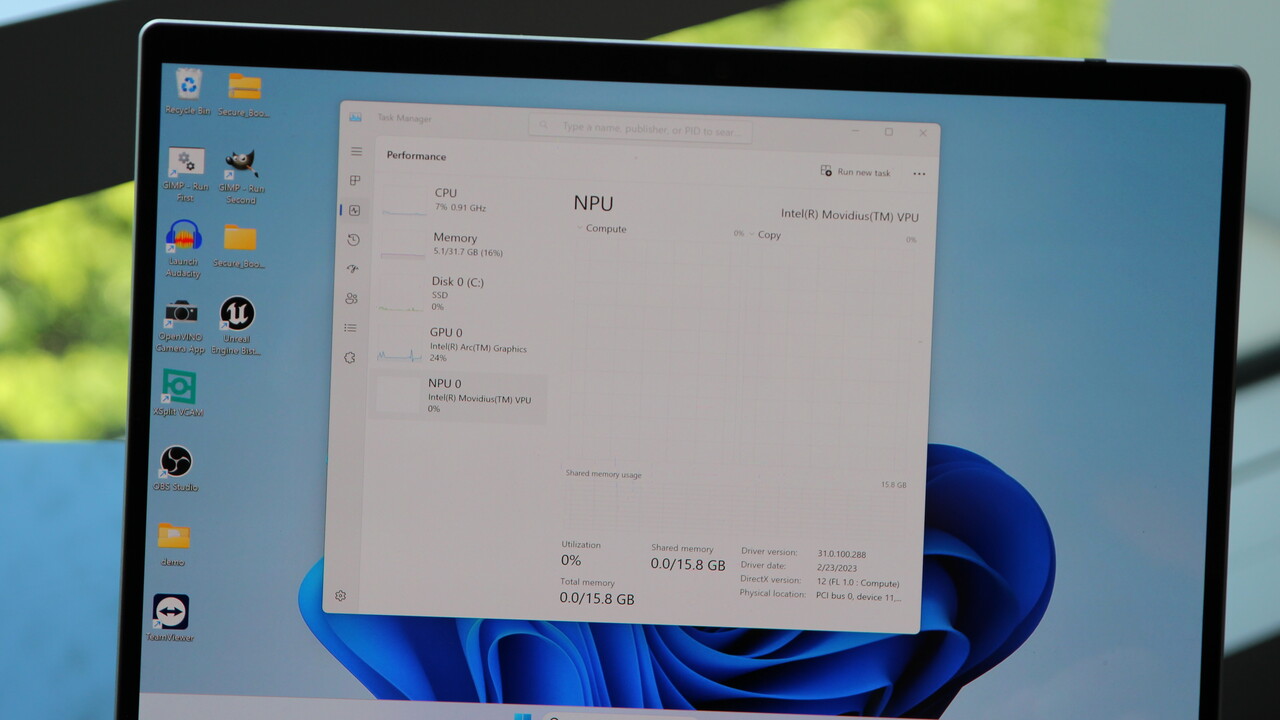

Adamantine-Cache erweitern wird, bleibt zudem auch noch eine offene Frage. Ich könnte mir vorstellen, dass man es eher vermeiden wird das Design zusätzlich zu verkomplizieren (

und zu verteuern) und es diesbezüglich eher der allgemeinen CPU-Mehrleistung überlässt hier zu überzeugen. Den übergroßen L4$ wird es ggf. nur bei CPU-Modellen mit großer tGPU geben, deren Aufgabe es sein wird eine dGPU überflüssig zu machen ... aber das bleibt letzten Endes abzuwarten. Intel hat mehr Ressourcen als AMD bzgl. der Produktdiversifikation ... wenn man den betreffenden Markt als zahlungswillig einschätzt, könnte es zudem auch Desktop-CPUs mit dem L4$ geben, wer weiß ...

) Weiterhin kommt hinzu, dass die Massenfertigung in 20A gerade erst mal mit ARL anlaufen wird, d. h. man wird gleichzeitig noch begrenzte Kapazitäten haben, die erst mit der Zeit ausgebaut werden, d. h. auch die Kapazitätsfrage könnte hier hineinspielen, sodass man noch einen weiteren Grund hat sich mit TSMC zu behelfen.

) Weiterhin kommt hinzu, dass die Massenfertigung in 20A gerade erst mal mit ARL anlaufen wird, d. h. man wird gleichzeitig noch begrenzte Kapazitäten haben, die erst mit der Zeit ausgebaut werden, d. h. auch die Kapazitätsfrage könnte hier hineinspielen, sodass man noch einen weiteren Grund hat sich mit TSMC zu behelfen.