7nm ab 2023 bei TSMC? Da müsste es ja schon 3nm geben bei TSMC. Hat Intel wohl nur noch den alten Salat bekomm der übrig bleibt. Und die Top Produkte komm dann gar nicht mehr von Intel also. Waia.

Ja 3nm wird es dann sicherlich geben bei TSMC in der HVM. Der Punkt ist, dass eine Nutzung von Intels Konkurrenten in 2023 eher unwahrscheinlich ist. AMD wird 3nm voraussichtlich nicht vor 2024 nutzten. Das ist schlicht eine Kostenfrage, denn die Entwicklung als auch die Fertigung dieser Designs wird nochmals deutlich teuerer und AMD ist noch zu klein um sich mit so einer kurzen Amortisierungphase bei Zen4 zu arrangieren.

Darüber hinaus spricht Intel immer noch davon einen Großteil der Produkte selbst zu fertigen, was schon bereits die Wirtschaftlichkeit diktiert, denn 7nm soll vollständig konkurrenzfähig zu TSMCs 5nm sein. Was sie hier genau extern fertigen lassen werden, bleibt abzuwarten, wenn jedoch bereits ein Design wie Meteor Lake ein massives MCM/Foveros-Desing sein soll, spielt das auch schlussendlich keine Rolle mehr, wo die Chipbestandteile herkommen. Bei AMD rümpft ja auch keiner die Nase, dass die nicht einmal imstande sind ihre Produkte selbst zu fertigen.

Am Ende entscheidet schlicht das Bilanzsheet, ob sie hier recht hatten. Hier wird man einfach die nächsten Jahre abwarten müssen, wie sich das bei denen Entwickelt.

Wobei Zen4 wohl schon in 5 nm erscheint. [...]

Nicht nur "wohl", sondern gar definitiv.

Zusagen zu Genoa und 5nm sind schon gut 1 Jahr alt und bisher ist nicht bekannt, dass AMD hier mit zwei unterschiedlichen CCD-Designs aufwarten wird. Und auch auf dem hinglänglich bekannten Roadmap-Sheet schreibt AMD explizit "

5nm", ganz im Gegensatz zu RDNA3, wo man lediglich unspezifisch von "

Advanced Node" spricht (

ich würde hier auf den N6 tippen, vermultich ebenfalls ein Kosten/Margenfaktor).

Intel ist erledigt. 2023 eine Kopie von Ryzen 3X00 ist doch arm.

Das sagen FBs und/oder H'er schon seit 2017 und es hat sich nichts bewahrheitet, eher im Gegenteil, Die letzten drei Jahre waren absolute Rekordjahre für Intel. Hast du noch mehr solche treffsichere Prognosen parat?

Darüber hinaus ist der Kopie-Vorwurf unbegründet und Intel "klebte Chips" schon deutlich vor Zen zusammen.

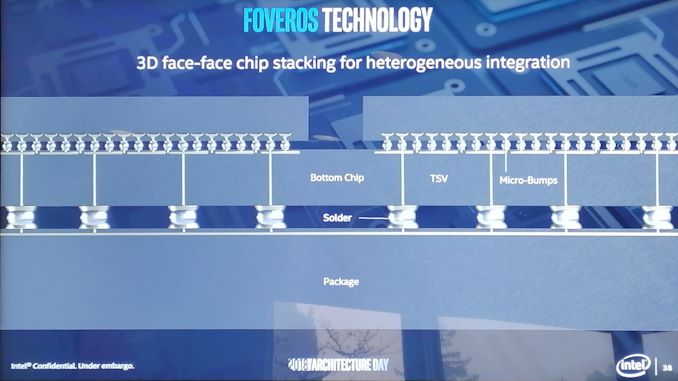

Intel ist bzgl. seiner Packaging-Technologien deutlich weiter als alles was AMD bisher nutzte. EMIB ist deutlich fortgeschrittener als das bisher genutzte IF-Konstrukt und Foveros ist per se ein Novum. Aktuell stünde AMD bestenfalls TSMCs CoWoS zur Verfügung, das jedoch lediglich ein fortgeschrittenes 2,5D-Packaging darstellt.

7nm im Zusammenhang mit Meteor Lake meint den Intel eigenen 7nm-EUV-Prozess.

Man möchte für gewisse Chips auch einen externen Node von TSMC nutzen, sagt aber nicht welchen. Aber sehr wahrscheinlich einen zum gegebenen Zeitpunkt aktuellen.

Grundsätzlich sind/waren Meteor Lake und auch der Server Granite Rapids SP für deren massiv-EUV-nutzende 7nm vorgehensehen (

zu dem Zeitpunkt ist das bereits ein 7nm+). Um flexibel zu sein, musste Intel jedoch frühzeitig Kapazitäten buchen, u. a. bei TSMC, d. h. die haben die nun so oder so und die werden die selbstredend auch irgendwie nutzen, denn bezahlen lassen wird sich die TSMC auf jeden Fall.

Beispielsweise hat Intel bereits in diesem Jahr absehbar kleine Kontingente in TSMCs 5nm, denn die brauchen sie (als Fallback) für Xe-HPC/Ponte Vecchio, denn der ist explizit für Intel's 7nm ausgelegt und TSMCs 7nm-Nodes sind daher nicht ausreichend für dessen Compute Tile.

Hier wird man einfach abwarten müssen. Wie schon zuvor erwähnt, dürfte das aber auch zukünftig eine untergeordnete Rolle spielen, wenn sie die Kapazitäten derart flexibel nutzen. Für 2023/24 würde ich eher vermuten, dass "der Fertigungsprozess" als solcher deutlich in der Hintergrund rückt und eher wieder architektonische Details in den Vordergrund rücken. AMD konnte hier einige Jahre von Intels selbstverursachtem Fertigungsrückstsand profitieren, mittelfristig wird sich der Schlagabtausch eher auf die designtechnischen Aspekt konzentrieren. Dass AMD vorerst on-the-edge mit dem teuersten, verfügbaren Node fertigt, ist in den nächsten Jahren eher nicht zu erwarten, denn man will die Marge steigern und nicht gleich wieder das Wachstum ausbremsen.

Mir ist nicht klar warum AMDs Änderung von 8 Kernen pro CCX ein Rückschritt sein soll.

Aber ich bin auch kein Redakteur.

Das "Problem", wenn man so will, war, dass der zweigeteilte CCX ein idealerweise separat zu berücksichtigendes 16+16 MB-Cache-Design aufwies und zusätzliche Latenzen mit sich brachte, denn nicht einmal alle Kerne auf einem CCD konnten direkt miteinander kommunizieren.

Zen3 löst das mit dem unified CCX/CCD deutlich besser und hier könnte man nun argumentieren, warum nicht gleich so, warum der Zwischenschritt mit Zen2? Die weiteren Optimierungen für Zen3 hätte man sich ja aufsparen können, aber wenigstens den CCX hätte man schon vorab zusammenlegen können.

Das kann ressourcentechnische Gründe gehabt haben und/oder auch schlicht vertriebstechnische Gründe, denn AMD, wie alle anderen Firmen auch, muss ja schließlich auch daran denken, wie man die Produkte von Morgen auch noch an den Mann und die Frau bringen kann. Und auch wenn ein Überspringen von Zen2 vielleicht wünschenswert gewesen wäre, in AMDs aktueller Situation ist ein In-den-Markt-bringen in schneller Abfolge deutlich vorteilhafter für deren Zielsetzung.

Zurück zum Artikel: Meteor Lake: Hybrid-Prozessor mit 7-nm-Chiplet-Design ab 2023 gegen Zen 4

Zurück zum Artikel: Meteor Lake: Hybrid-Prozessor mit 7-nm-Chiplet-Design ab 2023 gegen Zen 4.gif)