Rollora

Kokü-Junkie (m/w)

was der Grund war, warum ich geschrieben hab, dass es wohl kein Problem sein wird.ARM-Lizenzen kann man einfach kaufen.

Das stimmt natürlich, man kann fertige ARM Kerne verwenden.Und wenn man nicht, wie Apple, die Kerne selbst weiterentwickeln will, braucht man auch kein spezifisches Know-How. Implementiert kriegen die selbst chinesische oder russische Start-Ups und wie man beliebige Kerne einbettet und ordentlich vernetzt, das weiß AMD ja.

Dann hebt man sich halt aber auch nicht von der Konkurrenz ab.

Ich bin mir da grad nicht sicher ob ich das richtig verstehe, du meinst in einem modernen Kern mit modernen Verfahren sind bis 30% x86 exklusive Recheneinheiten (und Co?). Ich ging eher davon aus, dass das inzwischen ein verschwindend geringer Teil ist und der Rest recht allgemein funktioniert.Aber einfach nur x86 gegen ARM zu tauschen, bringt halt keine riesigen Leistungs- oder gar Effizienzfortschritte in den von AMD bedienten Marktbereichen. Der direkt mit x86 beschäftigte Decoder-Teil einer modernen CPU ist zwar eher 10 bis 15 Prozent groß und wenn man den zusätzlichen Aufwand bei der Sprungvorhersage, Scheduling im Backend mitzählt, der aus der größeren Bearbeitungslatenz von CISC-Befehlen resultiert, dann ist man sogar schnell bei den 30 Einsparpotenzial,

hmmm: ob nicht Intel das gerade versucht, diverse Kompatibilität wegzulassen und den x86 Teil zu verkleinern (wann auch immer das kommen wird) https://www.tomshardware.com/news/intel-ponders-transition-to-64-bit-only-x86s-architectureErst bei sehr kleinen CPUs hat ARM einen prinzipiellen Vorteil, denn der x86-Overhead lässt sich nicht beliebig verkleinern. Verglichen mit einem modernen .Little-Cluster sind auch E-Cores immer noch sehr mächtige und damit stromhungrige Rechenwerke.

bzw hier: https://www.phoronix.com/news/Intel-X86-S-64-bit-Only

Wenngleich ich nicht abschätzen kann wie viel man sich da spart.

Allerdings sollte in Homecomputern, Laptops und Co der Verlust von 16/32 Bit HW Support verschwindend geringe Folgen haben.

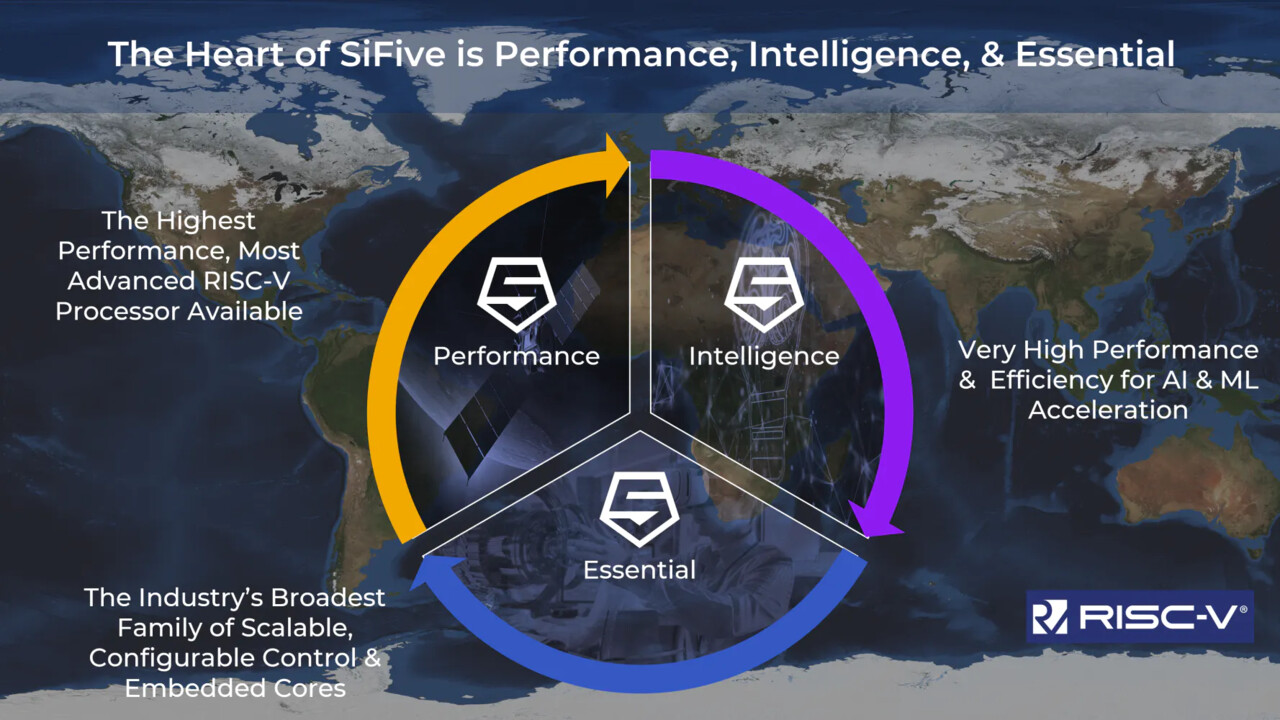

WER?SiFive sieht das nun anders.

Eingebundener InhaltYoutubeAn dieser Stelle findest du externe Inhalte von Youtube. Zum Schutz deiner persönlichen Daten werden externe Einbindungen erst angezeigt, wenn du dies durch Klick auf "Alle externen Inhalte laden" bestätigst: Ich bin damit einverstanden, dass mir externe Inhalte angezeigt werden. Damit werden personenbezogene Daten an Drittplattformen übermittelt.

Für mehr Informationen besuche die Datenschutz-Seite.

Aha irgendein Mensch der seine Meinung auf YouTube äußert. Background?

Und ja Du hast recht. 2 weitere Sätze meinerseits hätten das auch vermeiden können.

Und ja Du hast recht. 2 weitere Sätze meinerseits hätten das auch vermeiden können.