DaStash

PCGH-Community-Veteran(in)

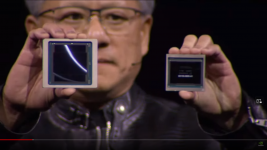

Danke, ich hatte das zwar noch im Hinterkopf war mir aber nicht mehr sicher. Ich bin gespannt wann das im Konsumer Markt Einzug erhält.MI300 ist eine MCM GPU mit mehreren verbundenen "Compute Dies".

Pro und Con wird man wohl erst zu Release des B200 prüfen können. Wenn ich raten soll: MCM hat höhere Latenzen, ist dafür günstiger als der Die-to-Die Ansatz. Ggf. kommen bei MCM auch weniger defekte GPUs am Ende raus.

MfG

.gif)