Jetzt ist Ihre Meinung gefragt zu AMD CPUs: Speicher-Flaschenhals von MCM-CPUs soll durch ausgelagerte Northbridge umgangen werden

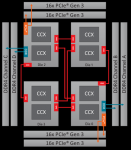

Der Flaschenhals bei der Speicheranbindung aktueller MCM-CPUs von AMD soll mit einem zentralen und separaten "System Controller" umgangen werden, der als zentrale Anlaufstelle für die umgebenden Dies dient. Gleichzeitig soll er zudem auch als Southbridge dienen. Wie sich das gestalten könnte, zeigt Twitter-Nutzer "The Retired Engineer".

Bitte beachten Sie: Der Kommentarbereich wird gemäß der Forenregeln moderiert. Allgemeine Fragen und Kritik zu Online-Artikeln von PC Games Hardware sind im Feedback-Unterforum zu veröffentlichen und nicht im Kommentarthread zu einer News. Dort werden sie ohne Nachfragen entfernt.

Zurück zum Artikel: AMD CPUs: Speicher-Flaschenhals von MCM-CPUs soll durch ausgelagerte Northbridge umgangen werden

Zurück zum Artikel: AMD CPUs: Speicher-Flaschenhals von MCM-CPUs soll durch ausgelagerte Northbridge umgangen werden

Der Flaschenhals bei der Speicheranbindung aktueller MCM-CPUs von AMD soll mit einem zentralen und separaten "System Controller" umgangen werden, der als zentrale Anlaufstelle für die umgebenden Dies dient. Gleichzeitig soll er zudem auch als Southbridge dienen. Wie sich das gestalten könnte, zeigt Twitter-Nutzer "The Retired Engineer".

Bitte beachten Sie: Der Kommentarbereich wird gemäß der Forenregeln moderiert. Allgemeine Fragen und Kritik zu Online-Artikeln von PC Games Hardware sind im Feedback-Unterforum zu veröffentlichen und nicht im Kommentarthread zu einer News. Dort werden sie ohne Nachfragen entfernt.

.

.